VCO在模擬射頻IC設計中的關鍵角色與挑戰(zhàn)——EETop社區(qū)視角下的技術探討

在半導體與集成電路設計領域,模擬射頻IC設計始終是技術前沿與難點所在,其中壓控振蕩器作為射頻系統(tǒng)的核心模塊,其性能直接決定了整個通信鏈路的品質。作為國內最大最火的半導體、集成電路設計社區(qū),EETop上關于VCO設計的討論,不僅反映了行業(yè)的技術熱點,也揭示了工程師們在嵌入式系統(tǒng)與電子電路設計中的實踐智慧。

一、VCO:模擬射頻IC的心臟

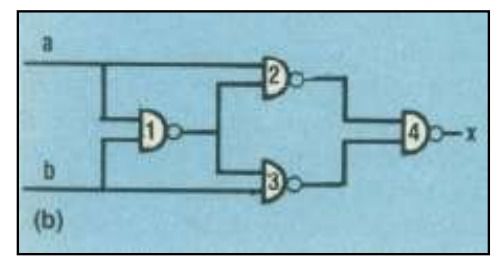

壓控振蕩器作為頻率合成器、時鐘恢復電路及調制解調器的關鍵部件,其相位噪聲、調諧范圍、功耗和面積等指標,一直是模擬射頻IC設計的重中之重。在EETop論壇上,資深工程師們常圍繞LC振蕩器、環(huán)形振蕩器等拓撲結構的優(yōu)劣展開激烈辯論。例如,LC振蕩器憑借其優(yōu)異的相位噪聲性能,在高頻應用如5G射頻前端中占據(jù)主導;而環(huán)形振蕩器則以更小的面積和更寬的調諧范圍,在低功耗物聯(lián)網(wǎng)芯片中備受青睞。

二、設計挑戰(zhàn)與社區(qū)智慧

在EETop的專題帖子中,許多設計師分享了VCO設計中的實際挑戰(zhàn):首先是工藝角偏差下的頻率穩(wěn)定性問題,尤其是在先進納米工藝下,器件變異對振蕩頻率的影響愈發(fā)顯著;其次是電源噪聲抑制,如何通過架構優(yōu)化(如差分結構)和版圖技巧(如屏蔽與隔離)來提升PSRR,成為熱議話題;如何在滿足低相位噪聲的同時實現(xiàn)寬調諧范圍,往往需要折衷設計,而社區(qū)中關于數(shù)字輔助校準、多波段切換等創(chuàng)新方案的討論,為初學者提供了寶貴經驗。

三、跨領域融合:從IC設計到嵌入式系統(tǒng)

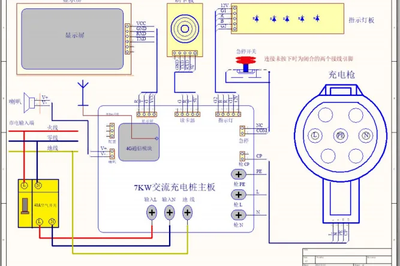

EETop社區(qū)的特點在于其跨學科性,VCO設計不僅涉及晶體管級模擬電路,還需與數(shù)字校準電路、嵌入式微控制器協(xié)同工作。例如,在軟件定義無線電中,VCO的頻率調諧需通過嵌入式處理器實現(xiàn)實時控制,這對IC設計者提出了系統(tǒng)級思維的要求。社區(qū)中不少成功案例展示了如何利用Verilog-A建模、協(xié)同仿真工具,將射頻前端與數(shù)字基帶無縫集成,體現(xiàn)了集成電路設計的整體化趨勢。

四、未來展望:技術趨勢與社區(qū)生態(tài)

隨著5G毫米波、Wi-Fi 7等技術的演進,VCO設計正向更高頻率、更低功耗邁進。EETop上關于硅基太赫茲振蕩器、基于新材料的諧振器設計等前瞻性話題,激發(fā)了行業(yè)創(chuàng)新活力。社區(qū)中豐富的學習資源——如開源設計項目、大牛經驗分享及在線課程——持續(xù)推動著國內IC設計人才的成長,形成了從理論到實踐的良性循環(huán)。

在EETop這一火熱的專業(yè)平臺上,關于VCO及模擬射頻IC設計的討論,不僅是技術細節(jié)的切磋,更是中國集成電路產業(yè)自主創(chuàng)新的縮影。從晶體管到系統(tǒng),從設計到流片,每一個帖子的背后,都是工程師們對極致性能的追求,以及對突破技術壁壘的執(zhí)著。

如若轉載,請注明出處:http://www.mhwap.cn/product/70.html

更新時間:2026-04-20 06:13:59